FRAISE : un projet open hardware pour simplifier la réalisation d’interfaces de contrôle.

C’est un environnement libre développé au sein de metalu.net, composé de cartes électroniques programmables à faible coût et d’un ensemble logiciel.

Cet outil vise à simplifier la réalisation d’installations robotiques, la construction d’interfaces de contrôle (pour la musique, la lumière, le Vjing…) ou tout autre assemblage de logiciels, de capteurs et d’actionneurs.

FRAISE trouve sa place dans de nombreuses créations d’artistes, dont certaines sont documentées sur le site metalu.net.

Apicula : lancement de la libération du FPGA Gowin GW1N

Le lecteur assidu de LinuxFr.org sait déjà sans doute ce qu’est un FPGA. Rappelons‑en cependant brièvement la définition.

Les FPGA sont des composants constitués de « champs de portes programmables ». L’idée est de graver un certain nombre d’éléments logiques simples sous forme de matrice et de laisser au développeur le loisir de reconfigurer à l’infini les connexions entre ces portes. Une fois les connexions configurées, on se retrouve avec un composant numérique sur mesure qui ne ressemble à aucun composant disponible chez les fournisseurs classiques. C’est très pratique quand on a besoin d’architectures bâtardes, ou quand justement on développe un composant numérique : ça permet de reconfigurer à l’infini pour déverminer et évaluer les performances.

Pepijn de Vos a effectué un stage pour Symbiotic EDA. Et l’ingénierie inverse du GW1N était son sujet de stage. Il a rendu son rapport avant Noël sur GitHub et a publié le code source du projet Apicula.

Vous voulez en savoir plus, lisez la suite…

Portable en Open Hardware, en bonne voie

Une carte mère en Open Source, ça existait déjà, mais une carte mère de portable en Open Source, je crois que c’est une première ! OK, il y a bien eu des projets dont la qualité n’intéressait pas le public.

Cette fois, il s’agit d’un ordinateur portable tout à fait apte à satisfaire chacun. Jugez donc :

Ce projet emmené par des passionnés est déjà bien avancé. Les schémas électroniques sont déjà disponibles sous CERN Open Hardware Licence v1.2 sur le projet GitLab oshw-powerpc-notebook/powerpc-laptop-mobo, et le travail a déjà commencé sur l’élaboration de la carte mère !

La réussite de ce projet permettrait non seulement d’avoir un ordinateur open source pour le public, mais aussi de permettre à d’autres d’utiliser ces travaux : des écoles de conception de matériel pour travailler sur ce type de produit, des sociétés qui peuvent réduire leurs coûts en partant du travail déjà effectué.

Alors, pensez à contribuer, soit en donnant du temps, soit en faisant une donation.

Sauver un disque dur mécanique

Nous savons tous qu’un disque qui a des secteurs défectueux n’est pas réputé fiable, que ça ne coûte rien un disque de remplacement, etc. Il n’empêche que c’est dommage de jeter le disque, certaines pannes sont contournables. Nous allons voir comment nous en servir pour nous familiariser avec la structure du disque, de ses partitions logiques (LVM) et de son formatage, tout en sachant que la fiabilité d'un disque abîmé reste très aléatoire et que la réparation sera précaire.

Il ne s’agit pas ici de récupérer des données (vous aviez des sauvegardes, n’est‑ce pas ?) mais uniquement de pouvoir réutiliser le disque. Voyons comment faire…

Diskio Pi : l’aventure continue

Il y a un an, je vous avais raconté l’historique de mon projet Diskio Pi à travers une dépêche, suivie d’un journal pour expliquer ce qu’était ce produit, proposé en financement participatif. Nombre d’entre vous ont été intéressés et ont aussi participé (merci à vous !) au financement Ulule de 2019.

La fabrication m’a pris un an, parsemée de doutes, de questions et de suggestions de la communauté, de tests et de galères à résoudre. Les livraisons ne devraient finalement pas tarder, j’explique ici les difficultés que j’ai rencontrées jusqu’à présent.

Parallèlement, et parce que j’ai eu quelques demandes urgentes, un nouveau financement est organisé afin de poursuivre la production, voire de l’intensifier. Ce nouveau financement se termine le 17 février 2020.

N. D. M. : un Raspberry Pi 3 A+ sera offert au centième contributeur (premier et deuxième financements confondus), si le financement actuel est un succès. Au terme du financement, l'objectif était dépassé (153%).

Kubuntu Focus : un portable optimisé

Kubuntu préinstallé sur un ordinateur récent, ça vous tente ? Avec l’aide de Tuxedo Computers, le projet Kubuntu Focus propose un petit monstre portable, préinstallé, optimisé, paramétré… pour convenir aux développeurs, graphistes et joueurs. Power out of the box comme ils disent. Plusieurs schémas de travail adaptés sont proposés, d’une façon originale : ils se lancent depuis le navigateur Web.

Kubuntu Focus livre seulement aux États-Unis et au Canada, pour le reste du monde, vous pouvez commander chez Tuxedo Computers.

La libération des FPGA et des ASIC bien engagée pour 2020

En début d’année 2019 se posait la question de savoir si ce serait l’année de la libération des FPGA. En ce début d’année 2020, essayons de faire un bilan.

FPGA, ASIC, HDL, RISC‑Ⅴ et PCB sont les chapitres que nous allons découvrir dans la suite de cet article. Si vous connaissez déjà ces sigles et acronymes, vous allez adorer ; mais si vous ne les connaissez pas, c’est indispensable car ces vocables sont à la base de la culture universelle de notre siècle.

Nous sommes actuellement arrivés à un moment clé pour le matériel informatique. Il en est au même point que le logiciel libre en était en 2000, quand il est devenu mature. Le mouvement est lancé et les projets deviennent utilisables. On ne rêve plus…

Automne, saison chaude chez Intel

Mardi 12 novembre, Arte diffuse le concert du Bal des enragés au Helfest 2019.

L’attention du public ainsi détournée, Intel en profite pour lancer une vague de correctifs, 77 correctifs, un grand nombre de CVE (des failles) y est dévoilé. Les failles concernent les processeurs eux‑mêmes (et microcontrôleurs) et les micrologiciels trop nombreux qui tournent dans vos cartes‐mères.

Simplifier la visualisation de chronogrammes

Le développement avec des langages de description matériel, le (System)Verilog par exemple, nécessite très souvent de visualiser les chronogrammes afin de vérifier le comportement du composant en développement. Ces chronogrammes sont générés par un simulateur tel qu’Icarus et GHDL, pour les versions libres, ou bien encore par ModelSim, VCS et consorts, pour les versions propriétaires.

GTKWave est la référence dans le monde du logiciel libre pour afficher les chronogrammes, mais il existe également autant d’afficheurs que de simulateurs propriétaires. De très nombreux développeurs ont sans doute été confrontés au côté rébarbatif de l’insertion à la souris des signaux à observer. GTKWave, ainsi que les simulateurs propriétaires, embarquent un interpréteur de langage Tcl afin de faciliter l’édition des signaux à observer avec, bien sûr, une syntaxe différente à chaque fois…

J’ai donc décidé de créer le module Python Wavedisp permettant de décrire hiérarchiquement les signaux à observer, ainsi que de procéder à la génération de scripts d’affichage pour différents outils de visualisation, dont GTKWave.

k1g1 : le premier FPGA Libre…

Cette dépêche est tirée d’un journal annonçant le k1g1, le premier FPGA libre… à sa connaissance.

Parmi les premiers commentaires du journal, on peut noter la promesse du succès mais pas avant dix ou vingt ans, des discussions sur les sociétés du domaine, l’évocation d’une puce de test, archipelago, le FPGA virtuel, etc.

Open Computer v0.1 : Preuve de concept d’un ordinateur portable modulaire sous GNU/Linux

Constatant qu’aujourd’hui les ordinateurs portables sont de plus en plus difficiles à réparer et à faire évoluer, nous avons décidé de remédier à cette situation : nous développons un ordinateur portable modulaire constitué de blocs contenant des pièces standards du marché. Sans inventer de nouveaux composants, nous réorganisons l’architecture matérielle d’un ordinateur portable. L’intérêt est de pouvoir changer soi‐même les pièces de son ordinateur en quelques secondes et sans risque de casse. Notre ordinateur n’est donc plus jetable, mais réparable, évolutif et écologique.

Comme vous pouvez le deviner, notre PC utilisera GNU/Linux, et dans la mesure du possible nous fournirons les plans en Open Hardware.

Un ASIC conçu intégralement avec des logiciels libres

Un ASIC (application‐specific integrated circuit, en anglais) est un circuit intégré d’électronique numérique conçu pour une application spécifique et qui ne peut être modifié une fois produit. Un ASIC est à mettre en opposition avec le FPGA qui lui est un circuit intégré d’électronique numérique que l’on peut reconfigurer à l’infini.

Les FPGA sont très liés aux ASIC. En effet, la plupart des outils utilisés en FPGA pour la synthèse HDL, la preuve formelle, le placement routage ou l’analyse des timings sont les mêmes que ceux à destination des ASIC. Seules les bibliothèques et les configurations changent. La grosse différence (de taille) avec les FPGA c’est que l’ASIC n’est pas reconfigurable, et les « frais d’initialisation » sont très élevés. Les délais de production sont également très longs (on parle en trimestres voire en semestres de délais).

Avec de telles contraintes, on comprend pourquoi les développeurs ne se mouillent pas trop avec des logiciels exotiques et restent sur ceux qu’ils connaissent. Vu les tarifs de production, le coût des licences des logiciels est assez négligeable. Pourquoi « grenouiller » avec des outils libres dans ce cas ?

Toutes ces contraintes n’ont pas découragé Tim Edwards de se lancer intégralement avec des outils libres dans la conception et la fabrication d’un microcontrôleur.

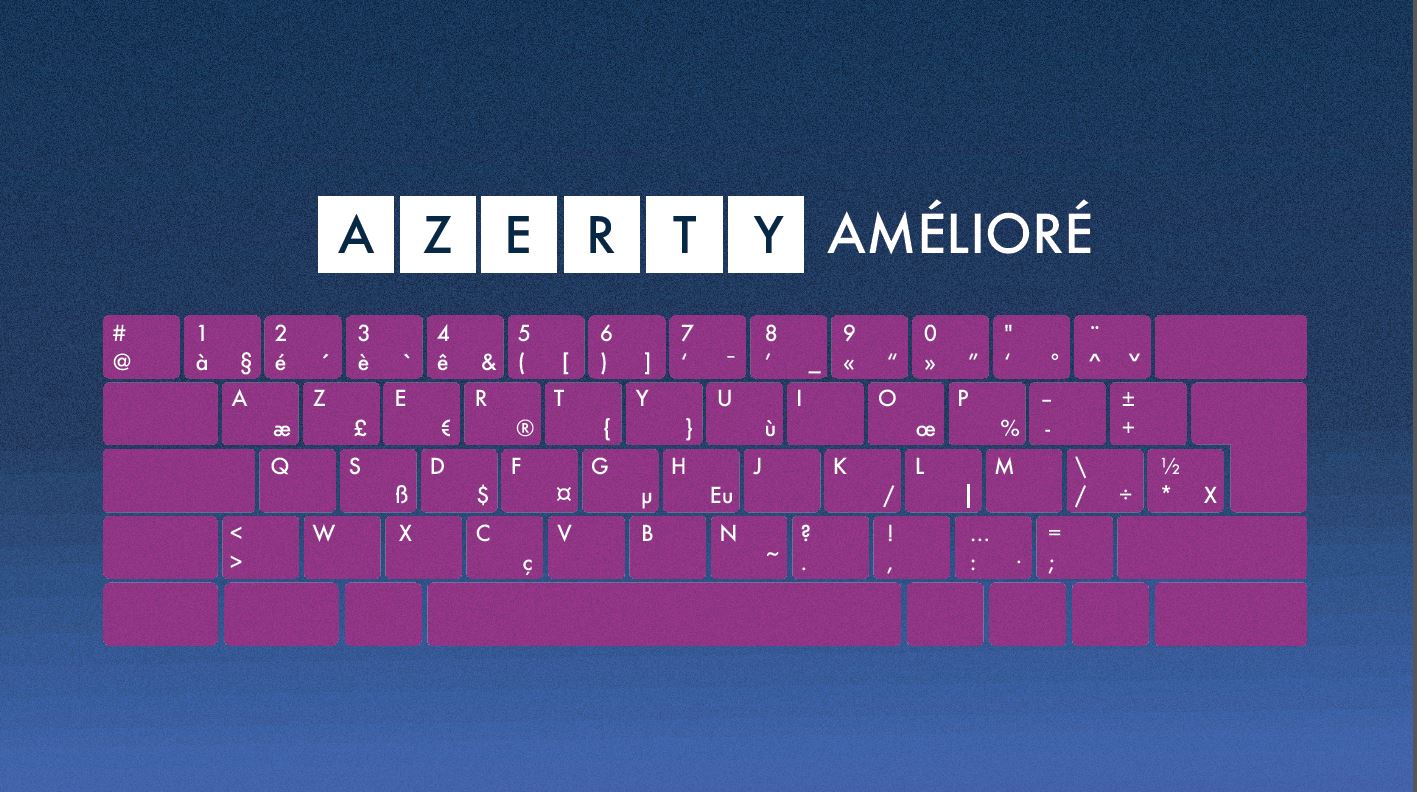

La norme française de dispositions de clavier a été publiée

L’AFNOR vient de publier la norme NF Z71-300 qui définit des dispositions clavier, une AZERTY et une BÉPO.

La disposition AZERTY ainsi normalisée permet de saisir tous les caractères nécessaires à l’écriture de la langue française, ainsi que d’autres langues européennes, en plaçant les symboles à des emplacements facilitant leur mémorisation.

Un thermomètre OSHW basé ESP8266

Dans la lignée du contrôleur de DEL, Leon Anavi est de retour avec un thermomètre, un produit matériel libre (ici on parle du circuit imprimé, pas des composants) de plus pour votre collection.

Le terminal libre Diskio Pi renaît de ses cendres

Après le financement participatif Kickstarter non réussi de décembre dernier, le projet Diskio Pi est de retour sur Ulule avec un objectif plus modeste. À l’heure qu’il est, le projet est déjà financé à hauteur de 328 %, ce qui est une très bonne nouvelle pour tous les libristes.

NdM : le financement participatif s'arrête le 3 mars, l'objectif initial est largement dépassé, le projet avance : le wiki et le site sont mis à jour, l'imprimante 3D est choisie, l'atelier de fabrication artisanale se met en place… il est encore temps de participer !

L'ambition du projet Diskio Pi est d'imaginer une nouvelle façon de tirer profit de nos données numériques, plus libre, tout en ayant la plus grande flexibilité matérielle et logicielle possible. C'est donc un hybride ordinateur-tablette, évolutif et Do it yourself : instructions, schémas et plans sont disponibles !

Sortie de la version 1.1 de Cocotb

Voici une excellente nouvelle pour la conception des composants électroniques numériques : la version 1.1 de Cocotb est sortie, la nouvelle vient de tomber sur la liste de diffusion de Cocotb.

C’est une grande nouvelle pour cette bibliothèque Python de co‐simulation HDL, sous licence BSD modifiée. En effet, malgré le travail de cinquante contributeurs, elle était bloquée dans sa version 1.0 depuis plus de quatre ans maintenant. La nouvelle organisation qui vient d’être mise en place devrait garantir la pérennité de Cocotb.

2018, l’année de la libération des processeurs ?

2018 aura été l’année du RISC-V. Ce jeu d’instructions libre existait bien sûr avant 2018, puisqu’il a été créé en 2010, mais c’est véritablement en 2018 qu’il aura pris son envol.

Entendons‐nous bien, le RISC-V, pour Reduced Instructions Set Computing version V, n’est pas un microprocesseur. C’est une définition du jeu d’instructions ainsi que des registres internes du processeur. Bref, cela doit être vu comme une standardisation open‐source du langage d’un processeur. Libre aux fondeurs de développer leurs architectures de processeur compatible RISC-V. Il définit les instructions assembleur et leurs formats (codage) mais il ne définit pas le nombre d’étages de pipelines, comment est gérée la prédiction de branche ni le format de bus de données et d’instructions. Tout cela relève de l’implémentation.

Financement participatif de la tablette tactile libre Diskio Pi

Diskio Pi, un écran tactile HD (en kit) compatible Raspberry Pi / Odroid en financement participatif.Le projet suscite beaucoup d’intérêt et d’articles de presse spécialisée depuis 2017. Un prototype a déjà été financé l’an dernier sur Ulule. Cet article raconte comment l’idée a germé et a grandi, pour arriver au financement participatif d’aujourd’hui.

NdM : financement non réussi (32794 € récoltés de 141 contributeurs, pour un objectif de 52096 €)

Sortie de Yosys Open Synthesis Suite 0.8

L’annonce a été faite mardi 16 octobre par W. Clifford : la version 0.8 de Yosis, un logiciel libre de synthèse Verilog est sortie.

Dans le processus de développement FPGA/ASIC la synthèse est l’étape de conversion du modèle matériel simulé en « netlist RTL », d’où l’on peut dériver le circuit réel.

Verilator 4.002

La version 4.002 de Verilator a été annoncée à la conférence ORConf2018 en Pologne.

Verilator est sans conteste le simulateur HDL open source le plus rapide du « marché ». Il permet de simuler des porte‐grammes écrits en Verilog synthétisable.

Un peu d’Open Hardware pour la rentrée (et beaucoup de LinuxBoot)

Après le rachat de Splitted-Desktop Systems par ITRenew, l’été a été plus que studieux, et il s’est déroulé entre le pays de l’oncle Sam et notre bon vieux continent (à ce propos si vous voulez un truc, évitez la Californie en été, c’est bourré de geeks auxquels il faut ajouter les touristes et, là, ça devient n’importe quoi sur à peu près tous les sujets).

La rentrée c’est la semaine prochaine et il est temps de reprendre un peu le travail, tout en mêlant le plaisir. Cette rentrée s’annonce chargée pour ceux qui aiment l’Open Hardware et GNU/Linux. Plusieurs événements à venir, qui tiennent à cœur à votre serviteur, sont à découvrir en deuxième partie de dépêche.

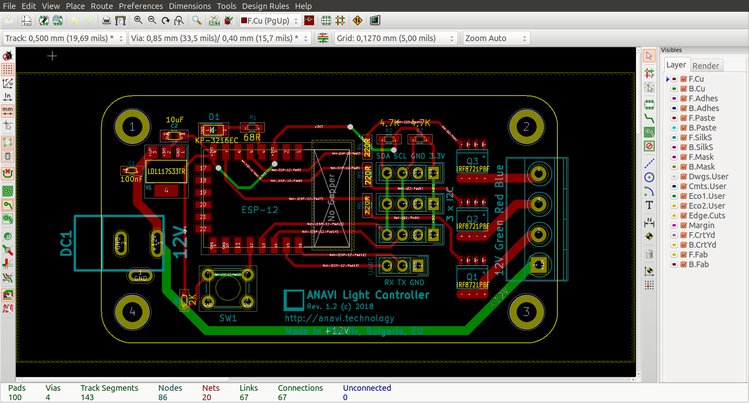

Microcontrôleur de DEL basé sur ESP8266

ANAVI Light Controller est une nouvelle carte matérielle libre pour contrôler un ruban de DEL (LED strip RGB). Ce projet est libre et conçu avec KiCAD, et disponible à l’achat à partir de 25 € jusqu’au 27 juin 2018.

La carte peut être utilisée de façon autonome avec le logiciel embarqué de démo en se connectant sur une page Web (MQTT d’Eclipse Paho). Mais passer par Internet via un broker MQTT public n’est peut‐être pas idéal pour tous, donc une autre solution est tout aussi envisageable via une passerelle locale (et optionnellement accessible à distance).

Naturellement, ce microcontrôleur (MCU) ESP8266 peut être aussi reprogrammé, c’est une alternative intéressante aux populaires Arduino car un bloc Wi‐Fi (pas libre ?) est intégré au MCU.

SymbiFlow, vers la synthèse libre pour la Série 7 de Xilinx

N. D. M : Le Verilog HDL est un « langage de description matériel de circuits logiques en électronique », le FPGA est un « circuit intégré logique qui peut être reprogrammé », Xilinx une entreprise américaine de semi‐conducteurs, et le bitstream est utilisé pour décrire une configuration à charger dans un FPGA.

Comme le projet IceStorm qui permet de générer des bitstreams à partir du Verilog vers les FPGA ICE40 de Lattice est maintenant très avancé, W.Clifford se lance avec d’autres dans la rétro‐ingénierie des FPGA de la Série 7 de Xilinx.

Pour cela, un nouveau projet nommé SymbiFlow est créé pour fédérer les différents outils permettant de développer autour des FPGA de Xilinx. L’objectif à terme étant d’intégrer également les ICE40 à SymbiFlow.

Le projet inclut un sous‐projet nommé sobrement Project X-Ray permettant de documenter les différents éléments du FPGA Artix7 sous forme de carte en ASCII et HTML. Ce sous‐projet vise également à fournir des outils permettant de piloter Vivado avec des designs simplistes pour sortir des statistiques sur les bitstreams générés et approfondir la documentation.

Un des gros changements de SymbiFlow par rapport à Icestorm est la volonté de migrer le placement‐routage de Arachne-pnr vers VPR. Un sous‐projet de VTR développé depuis bien plus longtemps que Arachne-pnr.

Vu le succès remporté par le projet IceStorm, avec la quasi totalité des FPGA ICE40 documentés ainsi que leurs timings, on peut espérer voir arriver rapidement une chaîne de développement libre pour les FPGA de la Série 7 de Xilinx. Et voir ainsi le développement open source sur FPGA devenir une réalité.

Le Linutop 6, le nouveau PC sans ventilateur

À l’occasion du salon Paris Open Source Summit 2017, la société Linutop a dévoilé son dernier mini‐PC livré avec la distribution Xubuntu : le Linutop 6.

Le choix du matériel est toujours sensible pour un noyau Linux. En effet, la disponibilité des pilotes peut être délicate comme Linus Torvalds a pu l’exprimer à propos, entre autres, de NVIDIA.

Il y a donc des points à surveiller, et si certains composants offrent des modes « legacy » qui sont compatibles avec des pilotes plus anciens, sans pour autant avoir toutes les fonctionnalités, ils permettent un usage direct de l’ordinateur sous GNU/Linux. C’est, par exemple, souvent le cas avec les cartes réseau.

Aussi, après de nombreux tests, le système monopuce Intel ATOM x5-Z8350 quadricœur à 1,9 GHz a été choisi. C’est une plate‐forme pour le monde industriel avec une durée de vie supérieure et, surprise, elle bien prise en charge par GNU/Linux.

NdM. : Vu que les questions à ce propos sont récurrentes à chaque dépêche de Linutop : la version téléchargeable est la version « Linutop OS Free », gratuite, dite « démo ». Les différences avec la version complète ne sont pas explicitées. Les licences des logiciels libres utilisés (bases Ubuntu ou Raspbian, et les éventuels logiciels libres modifiés) restent à clarifier. Il s’agit principalement d’un produit commercial dont les utilisateurs (plutôt professionnels) interagissent avec la société Linutop, plutôt qu’entre eux directement (a priori, pas de communauté ouverte avec des forums ou des listes de diffusion, d’après la discussion sur la précédente dépêche).

Qui est le coupable ? Le processeur ! Retour sur un bogue important des SkyLake & Kaby Lake Intel

Certains d’entre vous ont peut‐être vu passer l’information : les derniers processeurs Intel des familles Skylake et Kaby Lake sont victimes d’un bogue lorsque l’hyper‐threading est activé. On trouve par exemple un article sur Ars Technica, et Debian propose des instructions détaillées pour corriger le problème en mettant à jour le microcode (firmware) du processeur.

Cette dépêche propose revenir sur les événements qui ont mené à la découverte du problème. Xavier Leroy le décrit en détail dans un article sur le blog de l’équipe Gallium, dont je proposerai un résumé pour les lecteurs francophones.